## J.P.Morgan

# Innovation in Investment Banking Technology Field Programmable Gate Arrays (FPGAs)

A Field Programmable Gate Array (FPGA) is a silicon chip containing a matrix of configurable logic blocks (CLBs) that are connected through programmable interconnects. By combining optimized use of available silicon with fine-grained parallelism, sustained acceleration improvements of over 300x can be achieved across a range of vanilla and complex mathematical models. The current work is the first time that FPGA technology has been employed at this scale to accelerate computational performance anywhere in the finance industry.

#### **Power and Versatility**

- Can accelerate performance by between 100 and 1,000x across a range of mathematical models, with the ability to perform a task in less than a second

- Can be reprogrammed and precisely configured to compute exact algorithm(s) at the desired level of numerical accuracy required by any given application, unlike normal microprocessors whose design is fixed by the manufacturer

- Can be deeply pipelined to achieve maximum parallelism from arithmetic, algorithms and data streaming

## **Key Business Challenges**

- Reduce the execution time of existing applications to meet business and regulatory demands

- Decrease cost of running existing applications and developing new ones

- Provide fast, cost-effective extra computational capacity to address problems that are currently inextricable

- Achieve a step-change improvement in price-performance and end-to-end compute time across many applications

#### Key Benefits (Business/Clients)

- Competitive advantage to valuation, execution, risk management and complex scenario analyses by speeding up existing applications

- Lower cost of existing applications as hardware costs can be reduced by a factor between 100 and 1,000

- Ability to perform previously difficult calculations, such as complex trading strategies or risk evaluations of global portfolio simulations.

#### Technology Overview

- Low clock speed chips

- Maximal usage of available silicon resources

- Acceleration through use of fine-grained parallelism

- Reconfigurable hardware

- Silicon configurable to fit algorithm

#### LOB/Function(s) Impacted

- Credit & interest rates

- Equities & commodities

- Loan & mortgage modeling

- Finance & accounting

- High frequency trading

- Risk management & VaR

#### Industry/External Recognition

- Used by Cisco in all routers

- Simulation of real and theoretical systems

- Geophysics for oil and gas exploration

- Astrophysics & hydrodynamics

- Defense for cryptography

- Video games

- Genotyping

## J.P.Morgan

## **Functionality Overview**

Double precision floating point-capable FPGAs became commercially available in 2002, but it was the arrival of the Virtex 5 and 6 series chips from market leader Xilinx that really provided the scale required for the development of production-grade accelerated solutions. Using FPGAs in high performance compute solutions provides distinct advantages over conventional CPU clusters.

## **Operational Advantages**

- Significantly increases performance for two main types of applications: those based around highly complex mathematical models and those using simpler algorithms that can be massively parallelized

- Enables a dramatic increase in compute density per cubic meter by using FPGAs as computational accelerators

- Consumes around 1% of the power of a single CPU core

## **Performance Improvements**

- Performance improvements in the range 200-300x faster than the existing CPU cores used on the Compute BackBone (CBB) have been achieved in credit and interest rates hybrids businesses

- In equities, direct market access can run risk and loan stock at wire speed (3.5 micro secs) using a low-latency FPGA solution

- Benchmarked average throughput for J.P. Morgan's existing 40-node hybrid FPGA machine of 984MFlops/watt/cubic meter

- Potential standing at the top of the Green-500 ecological global supercomputer performance table

## **Development/Delivery**

#### Timeline

- Initial porting of an algorithm can vary from one to three months depending on complexity.

- Production capabilities then depend on the scale of the application and the scope and intensity of the testing and reconciliation cycle

#### Partners

- London-based Applied Analytics group: includes three technology and business specialists with extensive experience in developing and delivering high performance solutions across a range of asset classes, models and lines of business

- Maxeler Technologies: external consultants trained in Imperial College, Stanford and MIT research labs

## FPGAs at Work

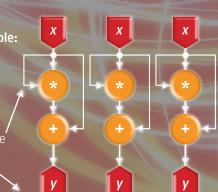

- An algorithm is implemented as a special configuration of a general purpose electric circuit

- Connections between prefabricated wires are programmable

- Function of calculating elements is itself programmable

- FPGAs are two dimensional matrix-structures of configurable logic blocks (CLBs) surrounded by input/output blocks that enable communication with the rest of the environment

#### A very simple sample:

## f(x) = 2x + x

Moving from a single calculation to a fine grained parallelism

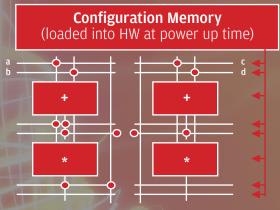

## A slightly more complex example:

e = (a+b)\*(c+d)

Migrating algorithms from C++ to FPGAs involves doing a Fourier Transform from time domain execution to spatial domain execution in order to maximize computational throughput. It's a paradigm shift to stream computing that provides acceleration of up to 1,000x compared to an Intel CPU.